HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

The area selection in the block and state machine diagrams can be toggled between ‘Enclosed’ (the selection model of EASE 9.2) and ‘All that is touched’ using the toggle selection button in the task buttons (outlined with the red border). When you are performing an area selection the cursor will indicate which selection type you use and can be switched by pressing the <space-bar>.

Textual notes can be attached to components, processes, ports, generics and states in a diagram, using the object’s context menu. The note will move with the object. The notes are not visible in the generated VHDL or Verilog code. Notes can be deleted by selecting them and pressing the <delete> key or selecting ‘Delete’ from its context menu.

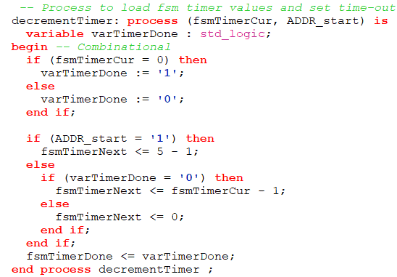

The state machines are extended with a timer process which can be activated in each state. The timer is a count-down timer loaded with either integer values, constants or generics (of type natural / integer). When an exit delay is specified for a state the timer is loaded upon entering the state and the state machine will not leave this state until the timer expires. The timer signal definitions are set in the FSM properties on the ‘Timer signals’ page of the FSM properties dialog.

The minimum counter delay is 2 clock cycles when the next state process is a clocked process and 1 cycle when the machine uses a combinational process. The timer maximum value should be specified by the designer when using constants or generics/parameters in the state exit delay.

Entity instantiations

A configuration specification can be generated in an architecture when

instantiating an entity using a component. When using direct instantiations or

configurations specification you can specify the architecture / configuration

that should be instantiated.

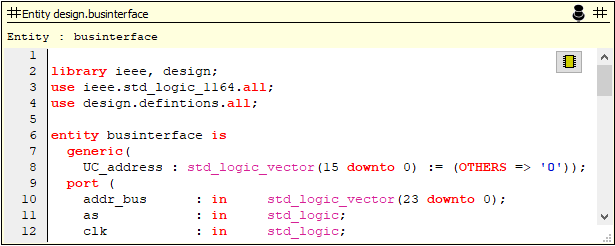

Library ‘work’

The project properties have a new option to instruct the generator to use 'work'

when referring to the local VHDL library. The option is set on the Project

properties dialog page VHDL. Using this option the generated VHDL code will not

change when you change the library name for references inside the library.

State machines

The reset transition of a statemachine can be set to synchronous or asynchronous

in the properties dialog of the reset transition. The synchronous reset

transition does no longer have a priority, but shows a closed square as start.

Truth tables

The reset of a clocked truthtable can be set to synchronous or asynchronous (in

the truth table properties dialog, ‘Clock behaviour’ page).

Verification

For verification messages originating from the HDL parsers it is now possible to

show the location of the error message in the generated HDL code using the

context menu in the verification results.

Tooltips can be automatic (timed) or on demand by pressing the F1 key. The behavior is set with the tooltip button in the main toolbar or the SHIFT-F1 accelerator key.

Tooltips can be pinned to the screen by pressing the ‘p’ key or by clicking on the pin when the tip is visible. The pinned tooltip will stay visible until the current project is closed or when you press the ESC key (or remove the pin). All pinned tips can be closed with the <SHIFT> ESC key. They can be moved on screen by dragging the header to the desired location. Text in the tooltip can be selected and copied to clipboard using the <ctrl-c> key.

The color scheme used by the Tcl console page in the console window and the foreground/background colors of the other table widgets in the console can now be explicitly set in the user options dialog on the Console page.

| Windows (64-bit only): | Windows 8.1 / 10 / 11 |

| Linux (64-bit only): | Should work with any recent distribution. Tested with RHEL 6 and RHEL 7. |

More

about EASE

More

about EASE Copyright © 2004 - 2026 HDL Works