HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

HDL Works has renamed ConnTrace to BoardTrace.

Modern microprocessors/microcontrollers have many user configurable IO pins to define the pin functionality. The processor configuration tools can usually generate a CSV file based report file describing the selected configuration. In BoardTrace can you can add a CSV report file as a virtual board and see how the configured processor pins are connected to the board.

This release supports microprocessors from NXP, TI and ST.

Have a look at the Processor page

to see what BoardTrace does with the processor information.

Simple resistors and capacitors in transmission lines make it difficult to view the actual connectivity between main components. With the netlist reduction option you can remove them from the netlist to view/verify the actual connectivity. You can also reduce all parallel capacitors or serial resistors to just 1 to increase performance.

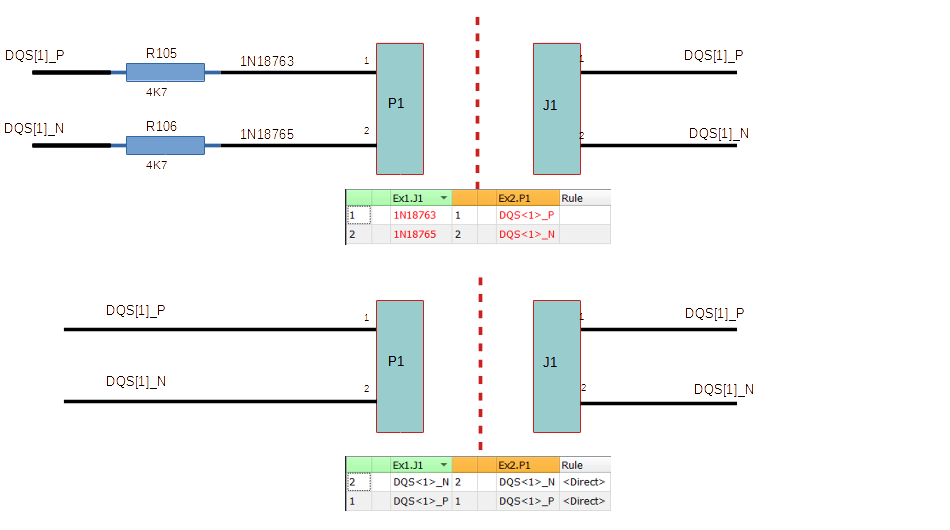

Without netlist reduction you would see that pins 1 and 2 of connector P1 connect to the signals 1N18763 and 1N18765 as shown in the connection trace. This makes verification difficult. After netlist reduction you would see them connected to DQS[1]_p and DQS[1]_N and they are easy to verify.

The removal of simple resistors and capacitors allows you improve verification in transmission lines from one board to another when such components are used. Netlist reduction is set for each board separately in the board properties dialog. The number of components removed is shown in the board tooltip. Using the context menu of a board in the PCB view you can open both the original and reduced netlist in the netlist viewer.

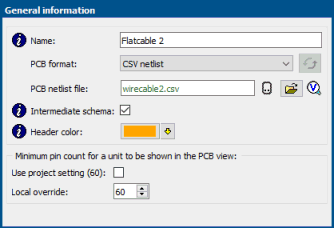

An intermediate board is a board present in your system to connect sub parts, but which doesn’t have functional names related to your other boards. An example of such a board could be wiring interconnect or a flat cable. When a board is declared to be an intermediate board the signal names on the nets are not used in the verification. This implies that names on intermediate boards are ignored during name matching and cannot be specified in the rules dialog.

The FPGA pinlist processing has changed for power pins, configuration pins and for unassigned user IO. For power pins we now use the pin label between '<' '>' characters as signal name instead of the voltage value and place the voltage value between brackets after the label. When no voltage is specified or recognized, the string <no voltage> is displayed.

Configuration and unassigned user IO are now displayed between ‘<‘ ‘>‘ characters to denoted they are not regular user IO.

The ODB++ netlist reader now support compressed components files.

Added fabrication format IPC-D-356. Although quite old it is often present in the Gerber data.

Each of the 3 views has a button to export the current view to a RFC-4180 compliant CSV file. The complete view with the visible rows and columns is exported. Cells that contain an icon are translated into the functional name of the icon.

Modules are no longer shown in the trace/netlist view. In cases where many modules were used things got too complex (too many schemas needed to be taken into account when creating/processing rules). Modules are shown in the connection details and it is possible to add rules specifically for the connection between the module and its schema.

BoardTrace 3.0 can be downloaded from our website using the link below.

Download

BoardTrace now

Download

BoardTrace now

BoardTrace

product info

BoardTrace

product info

Copyright © 2004 - 2025 HDL Works